数字电路·知识点梳理

2024-05-17 14:40:44 0 举报

AI智能生成

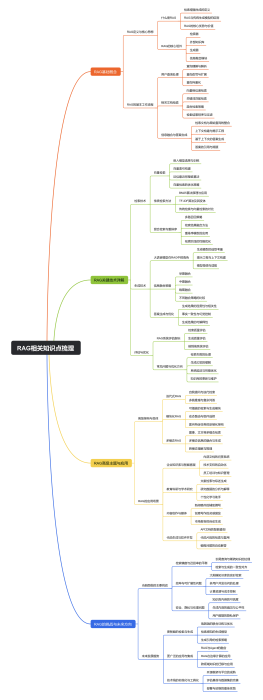

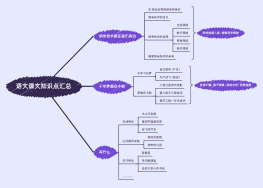

这是一份关于数字电路的知识点思维导图,包含了【基础理论】、【门电路】、【EDA】、【Verilog】

模板推荐

作者其他创作

大纲/内容

0 条评论

下一页