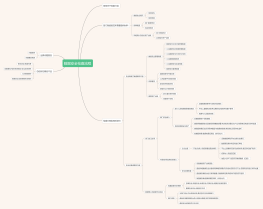

版图检查与验证

2016-12-20 17:25:08 0 举报

版图检查与验证是集成电路设计流程中的重要环节,主要目的是确保设计的电路图与实际制造的芯片在尺寸、形状和电气特性等方面完全一致。这一过程通常包括对版图进行详细的视觉检查,以识别并纠正任何可能的设计错误或偏差。同时,还会进行一系列的电学测试,如电流电压测试、电容电阻测试等,以验证电路的实际性能是否满足设计要求。通过版图检查与验证,可以有效地提高芯片的生产效率和质量,降低由于设计错误导致的生产成本和风险。