7 独立按键与矩阵键盘的FPGA驱动电路实现

7.1 按键及其工作模式介绍

7.1.1 按键抖动原理分析

7.1.2 硬件消抖动

7.1.3 软件消抖动

7.2 独立按键的FPGA驱动电路设计

7.2.1 独立按键电路设计

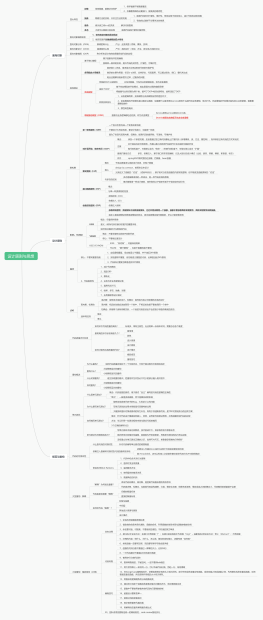

7.2.2 FSM状态机的Verilog HDL介绍

7.2.3 FPGA按键驱动设计方案1

7.2.4 FPGA按键驱动设计方案2

7.3 矩阵键盘的FPGA驱动电路设计

7.3.1 工作原理及电路设计

7.3.2 FPGA矩阵键盘驱动设计

8 “Hello World”的LCD1602显示驱动实现

8.1 LCD1602介绍及硬件设计

8.1.1 LCD1602字符液晶介绍

8.1.2 LCD1602硬件电路设计

8.1.3 LCD1602的时序及初始化分析

8.2 LCD1602的FPGA驱动电路实现

8.2.1 LCD1602的C语言实现方案

8.2.2 LCD1602的Verilog HDL实现方案

9 优化设计FPGA全局时钟管理模块

9.1 异步复位,同步释放机制

9.1.1 组合电路中的竞争-冒险

9.1.2 时序电路中的竞争-冒险

9.2 无PLL的全局时钟管理模块设计

9.3 Quartus II IP核介绍及PLL的定制

9.3.1 Quartus II IP核的介绍

9.3.2 PLL IP核的定制与分析

9.4 带PLL的全局时钟管理模块设计

11 基于FPGA与PC通信的UART串口设计

11.1 追根溯源透析串口通信

11.1.1 串口通信简介

11.1.2 串口波特率

11.1.3 串口协议分析

11.2 串口电路的设计

11.2.1 TTL转RS-232电路的设计

11.2.2 USB→UART转换电路设计

11.2.3 UART电路的调试

11.3 细说真正的任意分频

11.3.1 分频电路的重要性

11.3.2 任意频率发生器原理

11.3.3 任意频率发生器的验证

11.4 串口通信的硬件实现

11.4.1 uart_receiver接收模块的设计

11.4.2 uart_transfer发送模块的设计

11.4.3 PC2FPGA UART联调测试

12 基于FPGA的VGA驱动显示设计

12.1 VGA接口、时序及驱动电路设计

12.1.1 VGA接口介绍

12.1.2 VGA时序分析

12.1.3 RGB三原色模型

12.1.4 VGA驱动电路设计

12.2 VGA驱动的FPGA实现

12.2.1 VGA驱动时序电路的设计

12.2.2 任意分辨率的VGA显示控制器设计

12.3 “Hello World”的VGA显示驱动实现

12.3.1 “Hello World”字模的提取

12.3.2 C2Mif软件的介绍与Mif文件的生成

12.3.3 VGA字符显示的FPGA实现

13 基于SDRAM的VGA显示控制器的设计与实现

13.1 跨时钟域数据交互

13.2 SDRAM的介绍及其控制器的移植与优化

13.2.1 SDRAM的特性及时序驱动介绍

13.2.2 SDRAM的硬件驱动电路设计

13.2.3 SDRAM控制器的移植与优化

13.2.4 Sdram_Control_2Port的封装与协议制定

13.3 基于SDRAM的VGA显示控制器的实现

14 基于OV7725的摄像头视频图像采集系统

14.1 系统框架设计思路分析

14.1.1 系统框架分析

14.1.2 算法的实现流程

14.2 OV7725摄像头介绍与视频采集实现

14.2.1 CMOS摄像头的简介

14.2.2 OV7725的特性介绍及驱动电路设计

14.2.3 OV7725 SCCB接口及寄存器介绍

14.2.4 OV7725感光阵列与视频时序分析

14.2.5 OV7725寄存器I2C初始化设计

14.2.6 OV7725的视频采集模块设计

14.3 OV7725视频图像显示的实现

14.4 本章小结

15 基于FPGA的系统设计

15.1 FPGA芯片选型

15.2 FPGA的与众不同——PCB布局在设计原理图之前

15.3 存储器的选型

15.4 FPGA外围器件的选择与设计

15.4.1 电阻

15.4.2 电容

15.4.3 磁珠

15.4.4 保险丝

15.5 基于核心板的系统设计

15.6 基于低功耗系统的电源选型

15.7 高速系统的PCB设计要点

15.7.1 结构布局

15.7.2 电路板的多层设计

15.7.3 过孔设计要点

15.7.4 防止串扰的布线原则

15.7.5 差分线布线原则

15.7.6 开关电源PCB设计要点

15.8 本章小结

16 基于高速相机的嵌入式视觉处理系统设计

16.1 视觉处理系统概述

16.2 嵌入式视觉处理系统结构设计

16.3 芯片选型

16.4 基于Camera Link工业相机接口的硬件设计

16.5 基于Camera Link接口的FPGA程序设计要点

16.6 基于VGA接口的图像的实时缩小与算法结构

16.7 FPGA与DSP的协同工作模式

16.8 乒乓操作的进阶——零延时数据传输

16.9 系统调试

16.10 本章小结

2 Quartus II 13.0套件的下载及安装

2.1 写在前面的话

2.2 Quartus II 13.0软件下载

2.3 Quartus II 13.0组件安装

2.4 Quartus II 13.0 Device安装

2.5 USB Blaster下载器驱动程序的安装

3 Verilog HDL设计与Testbench文件架构

3.1 Verilog HDL设计

3.1.1 Verilog HDL与VHDL的对比

3.1.2 Verilog HDL的发展

3.1.3 Verilog HDL代码设计风格

3.2 Testbench文件架构

3.2.1 Testbench的介绍

3.2.2 Testbench代码设计风格

3.3 Quartus II工程目录文件夹的定制

4 MAX II CPLD/Cyclone II/IV FPGA PCB Layout设计

4.1 浅谈PCB Layout

4.2 MAX II CPLD核心电路设计

4.2.1 MAX II CPLD背景及简介

4.2.2 EPM240T100C5N设计需求研究及分析

4.2.3 EPM240T100C5N核心板原理图设计

4.2.4 EPM240T100C5N核心板布局布线

4.3 Cyclone II FPGA核心电路设计

4.3.1 Cyclone II FPGA背景及简介

4.3.2 Cyclone II数据手册解读与EP2C8Q208C8N的设计研究

4.3.3 EP2C8Q208C8N核心板原理图设计

4.3.4 FPGA核心板Layout注意事项

4.4 Cyclone IV FPGA核心电路设计

4.4.1 Cyclone IV FPGA简介

4.4.2 Cyclone IV FPGA数据手册分析与EP4CE6E22C8N的设计研究

4.4.3 Cyclone IV FPGA核心电路设计

4.5 FPGA/CPLD电路焊接、调试经验总结

4.6 本书配套FPGA开发平台硬件介绍

4.6.1 VIP_Board 3.0硬件资源介绍

4.6.2 VIP_Board 3.0相关外设实物介绍

5 4位计数器的设计与仿真验证

5.1 写在前面的话

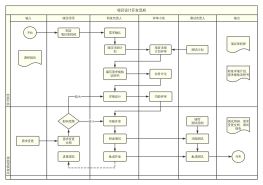

5.2 FPGA/CPLD开发流程

5.3 基于Quartus II 13.0的4位计数器设计流程

5.3.1 Quartus II 工程的创建

5.3.2 4位计数器的逻辑电路设计

5.3.3 Quartus II编译流程与工程设置分析

5.4 基于Modelsim-Altera 10.1d的4位计数器仿真验证流程

5.4.1 关于FPGA设计的各种仿真概念分析

5.4.2 Modelsim版本的简要介绍

5.4.3 Modelsim工程的创建

5.4.4 Testbench激励文件的编写

5.4.5 Modelsim波形的仿真与分析

5.5 设计思路的验证与总结