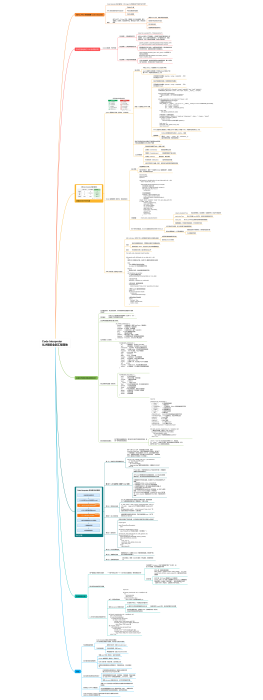

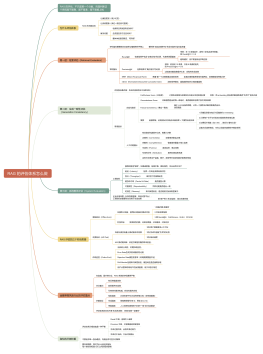

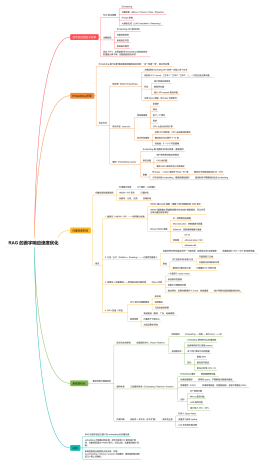

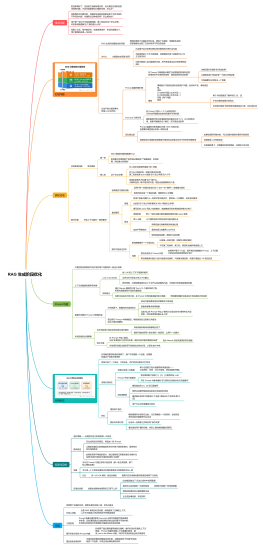

并发_JMM与并发三大特性

2023-03-29 15:01:13 14 举报

AI智能生成

JMM,并发

模版推荐

作者其他创作

大纲/内容

0 条评论

下一页